All of these screenshots come from BITS version 300; minor variations may occur in newer versions, but major changes or new features will result in an update to this page.

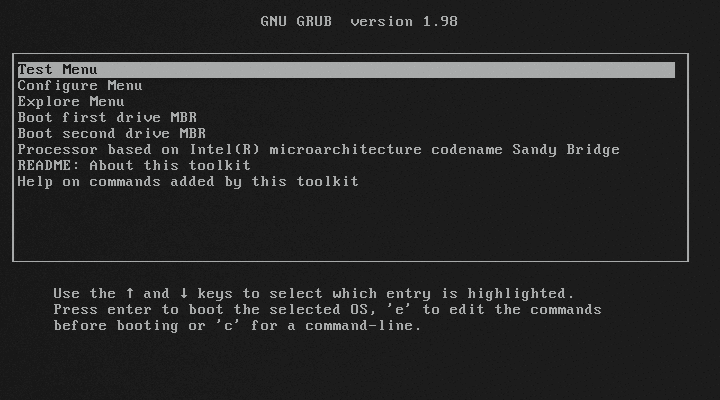

Main Menu

Notice that BITS automatically detected the processor type. From here, you can run the validation tests, change the configuration, run the exploratory tools, boot your system's OS via the MBR, or read some documentation.

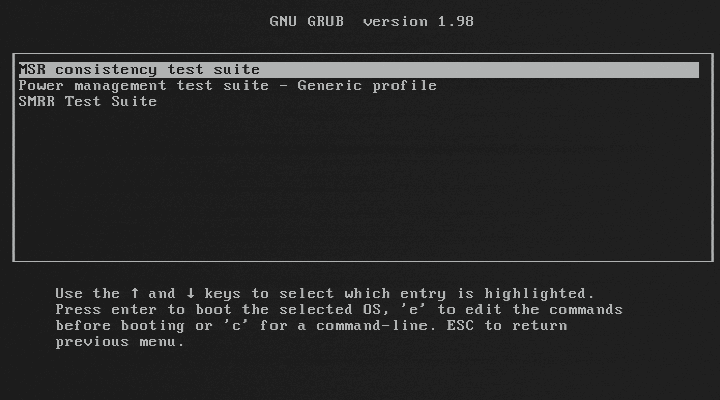

Test Menu

The test menu shows all of the pass/fail tests BITS can run on the system. On this system, BITS can check the CPU's model-specific registers for consistency across all CPUs, check how the BIOS configured power management, and check that the BIOS properly configures the system management range register (SMRR).

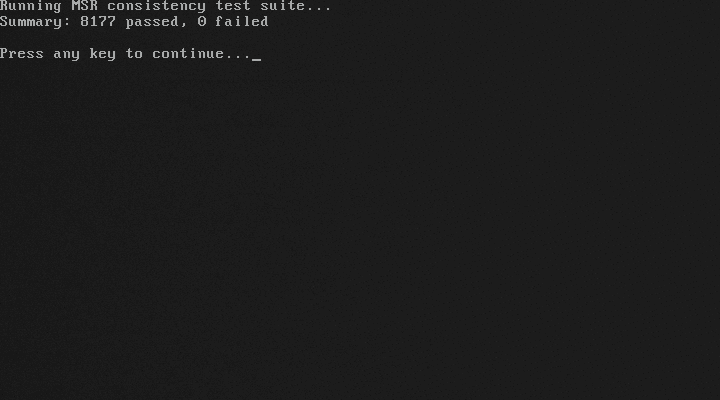

MSR Consistency Test

BITS can compare the CPU's model-specific registers for consistency between all CPUs on a system, which catches BIOS bugs involving incomplete initialization on SMP systems; some BIOSes fail to configure all CPUs identically, or unintentionally run configuration on a subset of CPUs.

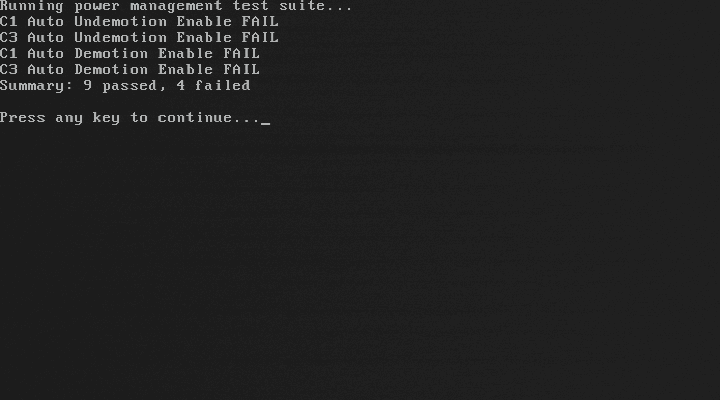

Power management test suite

BITS checks how the BIOS configured the various CPU and chipset registers related to power management, and verifies that it matches Intel's recommended configuration. Notice that this system fails to properly configure C-state auto-demotion and auto-undemotion.

Also notice that BITS defaults to only showing test failures, not test passes; this makes it easier to concentrate on fixing bugs.

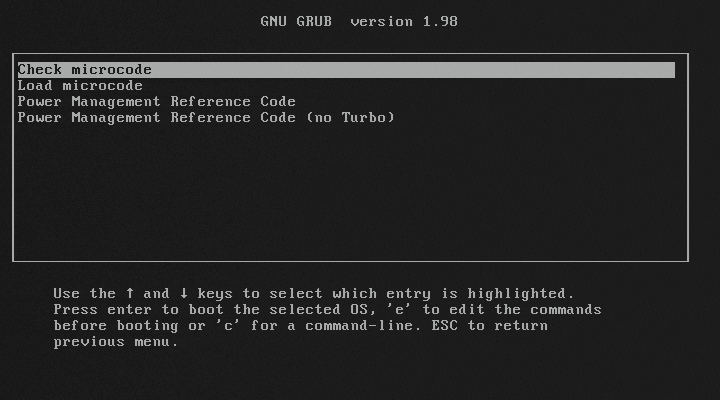

Configure Menu

The configure menu provides options to modify the system's configuration temporarily for the current boot; all such changes will go away at the next system reset, but you can boot an OS with these temporary settings in place.

On this system, BITS can run the power management reference code to configure CPU power management and write the ACPI tables. BITS can also check or update the CPU microcode.

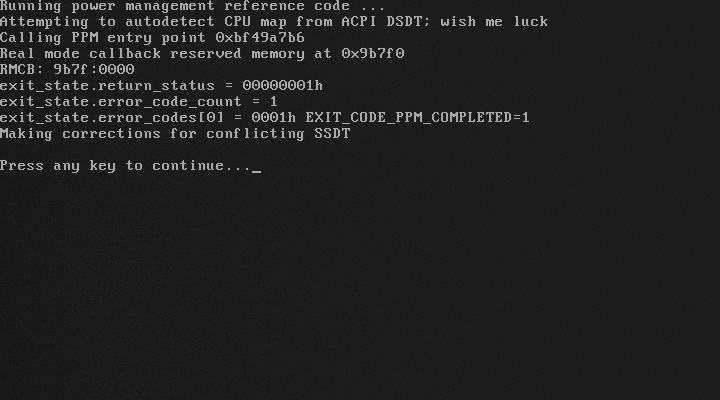

Power Management Reference Code

BITS can run the same power management reference code that Intel supplies to BIOS vendors, to override your BIOS's power management configuration with a known-working configuration. This sets various CPU configuration registers, and replaces the corresponding BIOS-supplied ACPI tables.

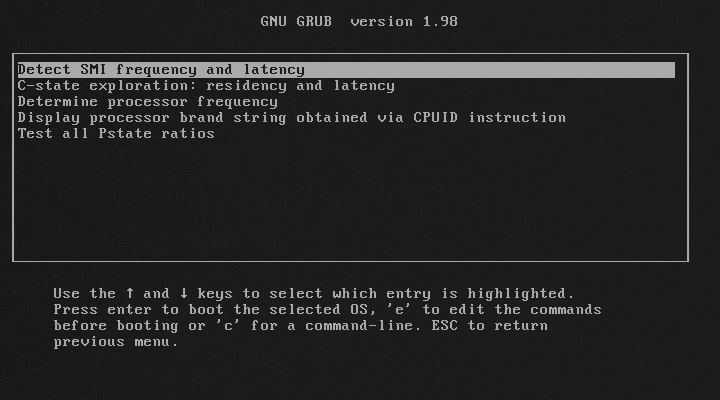

Explore Menu

The explore menu provides experimental tools to collect and display information, as well as some tests which do not yet have a definitive PASS/FAIL and thus do not appear in the test menu.

On this system, BITS can check P-state usage and C-state residency, detect the frequency and latency of BIOS system management interrupts (SMIs), and display the processor's frequency and brand string.

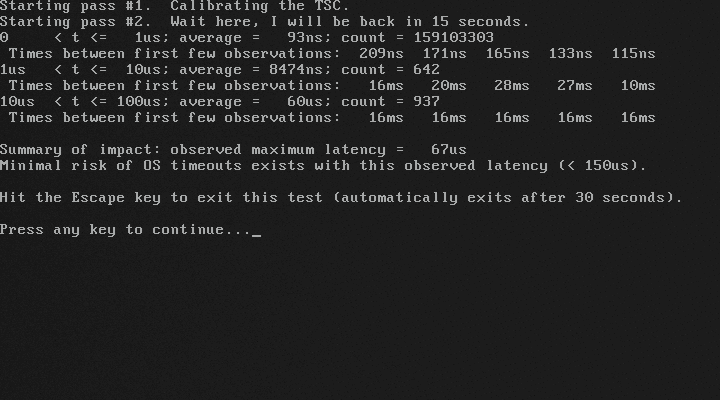

SMI frequency and latency

BITS can detect system management interrupts by watching for large gaps in time between successive values of the time-stamp counter. This tool shows the average duration of SMIs (grouped by orders of magnitude), the time between a few SMIs in each group, and the worst-case latency observed.

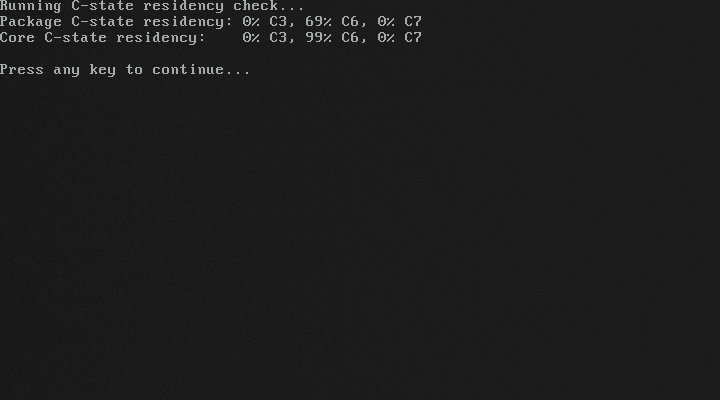

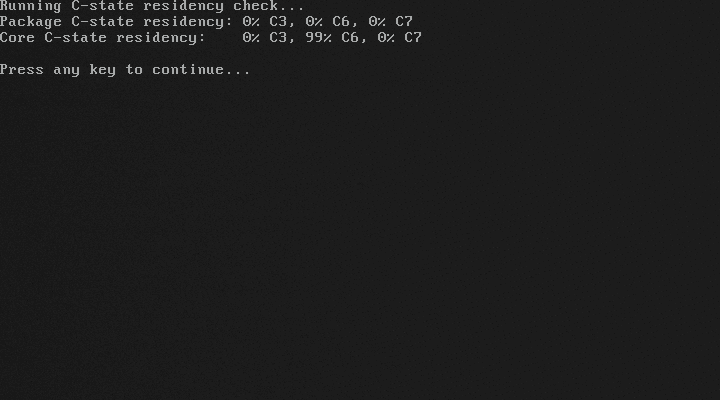

C-state residency - a case study

This test checks how long a CPU core and the entire processor package spend in C-states (sleep states), by directly checking the CPU's residency counters. Notice that on this system, no package C-state residency occurs; the BIOS has limited package C-states.

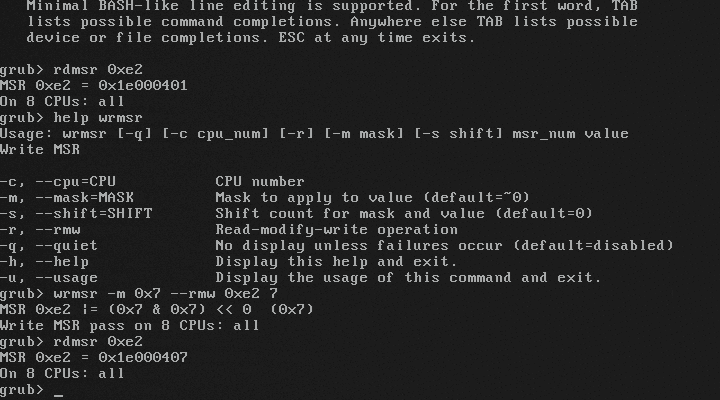

The Intel power management reference code would fix this issue. However, you can also run all of the BITS functionality from the GRUB command line, via the various new commands that BITS adds. So, let's experiment with that instead:

Via the rdmsr command, we see that the BIOS has limited package C-states by setting MSR 0xE2 bits [2:0] to 1. However, this BIOS did have an option to disable locking of that register, and using that option turned off the lock bit (bit 15). So, we can fix it via the wrmsr command, and now we get package C-states: